SSM-2300

8-CHANNEL MULTIPLEXED SAMPLE-AND-HOLD

Precision Monolithics Inc

# **FEATURES**

- On-Chip 1:8 Demultiplexer, 8 Sample-and-Hold Capacitors and 8 Output Buffers

- Saves Space, Reduces System Cost

- . Output Buffers Stable for C, ≤ 500pF

- Output Swing Includes Negative Supply

- TTL and CMOS Compatible Logic Inputs

- 5 to 18 Volts Total Supply Operation

- Low Cost

## **APPLICATIONS**

- Automatic Test Equipment

- Process Control and Monitoring Systems

- Audio and Video Systems

# ORDERING INFORMATION

| PACKAGE  | OPERATING      |  |  |

|----------|----------------|--|--|

| PLASTIC  | TEMPERATURE    |  |  |

| 16-PIN   | RANGE          |  |  |

| SSM2300P | -25°C to +75°C |  |  |

# **GENERAL DESCRIPTION**

The SSM-2300 is an eight-channel CMOS multiplexed sampleand-hold device designed for voltage level distribution in uP controlled systems. On-chip functions include an 8-channel demultiplexer, 8 sample-and-hold capacitors and 8 output buffers. This function saves valuable board space and reduces system cost where multiple voltage levels are required.

The SSM-2300 can operate from single or dual supplies with both TTL and CMOS logic compatibility. Useful for adjusting amplifier offsets or VCA gains, one or more SSM-2300s can be used with a single DAC to provide multiple set points within a system. Applications are in ATE, audio and video, process control and monitoring systems.

For improved performance and system upgrade, request the PMI SMP-08 data sheet.

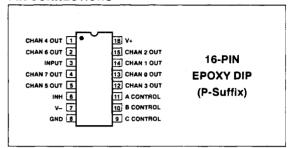

# PIN CONNECTIONS

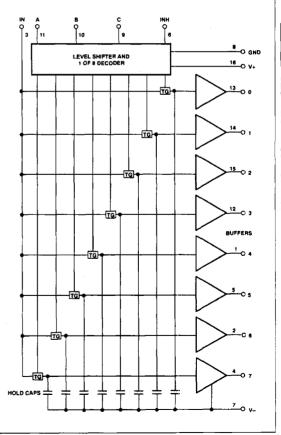

# **FUNCTIONAL DIAGRAM**

2/90, Rev. B

# **ABSOLUTE MAXIMUM RATINGS**

| Total Supply Range                                             | 18V             |

|----------------------------------------------------------------|-----------------|

| Positive Supply (V+ - V <sub>CND</sub> )                       | 18V             |

| Positive Supply $(V+-V_{GND})$<br>Negative Supply $(VV_{GND})$ | –10V            |

| Storage Temperature Range                                      |                 |

| P Package                                                      | -65°C to +150°C |

| Lead Temperature Range (Soldering, 60 sec)                     | 300°C           |

| Junction Temperature                                           | 150°C           |

| Operating Temperature Range                                    | -25°C to +75°C  |

|                                                                |                 |

| PACKAGE TYPE           | Θ <sub>βA</sub> (Note 1) | e <sub>jc</sub> | UNITS |  |

|------------------------|--------------------------|-----------------|-------|--|

| 16-Pin Plastic DIP (P) | 82                       | 39              | °C/W  |  |

#### NOTE

# ELECTRICAL CHARACTERISTICS at V+ = +15V, V- = GND, T<sub>A</sub> = +25°C, unless otherwise noted.

|                                |                      |                             |     | SSM-2300 |      |       |

|--------------------------------|----------------------|-----------------------------|-----|----------|------|-------|

| PARAMETER                      | SYMBOL               | CONDITIONS                  | MIN | TYP      | MAX  | UNITS |

| Supply Current                 | ı <sub>s</sub>       |                             | 2   | 4        | 8    | mA    |

| Positive Supply Voltage        | V+                   | (V+ - V <sub>GND</sub> )    | 5   | -        | 18   | v     |

| Negative Supply Voltage        | V                    | (VV <sub>GND</sub> )        | -10 | -        | 0    |       |

| Logic High (A, B, C, INH)      | V <sub>INH</sub>     | See Table 1                 | 6   | -        | _    | ٧     |

| Logic Low (A, B, C, INH)       | VINL                 | See Table 1                 |     | -        | 0.8  | ٧     |

| Channel Select Time            | ton .                |                             | -   | 300      | -    | ns    |

| Channel Deselect Time          | t <sub>OFF</sub>     |                             | -   | 300      | -    | ns    |

| Inhibit Recovery Time          | t <sub>INH</sub>     |                             |     | 150      | -    | ns    |

| Buffer Offset                  | Vos                  | 0 < V <sub>IN</sub> < +13V  | -   | 8        | 50   | mV    |

| Hold Step                      | V <sub>HS</sub>      | 0 < V <sub>IN</sub> < +13V  | -   | 4        | 8    | mV    |

| Acquisition Time               | t <sub>A</sub>       | 0 < V <sub>IN</sub> < +13V  | _   | 1        | _    | μs    |

| Settling Time                  | ts                   | 0 < V <sub>IN</sub> < +13V  | -   | 2        | -    | μs    |

| Droop Rate                     | dV <sub>CH</sub> /dt | 0 < V <sub>IN</sub> < +13V  | -   | 500      | 1500 | mV/s  |

| Output Source Current          | SOURCE               | 0 < V <sub>IN</sub> < +13V  | 1.2 | -        | -    | mA    |

| Output Sink Current            | Isink                | V <sub>OUT</sub> = V- = GND | 0.5 | -        | -    | mA    |

| Input/Output Voltage Range     | V <sub>IN</sub>      | $R_L = 10k\Omega$ to GND    | Ö   | -        | 11   | V     |

| Maximum Output Capacitive Load | C <sub>L MAX</sub>   |                             | -   | 500      | -    | pF    |

Specifications subject to change; consult latest data sheet.

# **SIGNAL INPUT (PIN 3)**

The signal input should be driven by a low impedance voltage source such as the output of an operational amplifier. The op amp should have a high slew rate and fast settling time if the SSM-2300's fast acquisition time characteristics are desired. As with all CMOS devices, all input voltages should be kept within range of the supply rails (i.e.,  $V- \le$  inputs  $\le V+$ ) to avoid latch-up.

If single supply operation is desired, an op amp such as the OP-21, OP-80, or OP-90 with input and output voltage compliance including GND, can be used to drive pin 3. Split supplies, such as  $\pm 7.5$ V, can be used for the SSM-2300 and the above mentioned op amps.

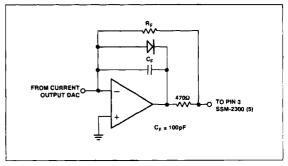

If the op amp driving pin 3 is powered by dual supplies, the circuit shown in Figure 1 should be used to avoid latch-up due to negative transients during power-up. The addition of a small capacitor as shown may be useful in preventing a large false hold step.

FIGURE 1: DAC Interface Circuit (SSM-2300 Single Supply, Op Amp Driver Split Supply)

Θ<sub>jA</sub> is specified for worst case mounting conditions, i.e., Θ<sub>jA</sub> is specified for device in socket for P-DIP.

# LOGIC INPUTS (PINS 6, 9, 10 AND 11)

For V+ supplies up to  $+7.5 \,\text{V}$ , logic inputs can be driven by TTL or CMOS. For V+ (of the SSM-2300) from  $+7.5 \,\text{V}$  to  $+12 \,\text{V}$ , TTL outputs should add pull-up resistors to the  $+5 \,\text{V}$  logic supply. For V+ of  $+12 \,\text{V}$  or greater, CMOS logic should be used (see Table 1).

TABLE 1: Control Input Switch Points (Volts)

| V+  | GND | V    | V <sub>IH</sub> | V <sub>IL</sub> |

|-----|-----|------|-----------------|-----------------|

| 5   | 0   | -5   | 2.4             | 0.8             |

| 5   | 0   | -10  | 2.4             | 0.8             |

| 3   | 0   | -12  | 2               | 0.8             |

| 7.5 | 0   | -7.5 | 3               | 0.8             |

| 15  | 0   | 0    | 6               | 0.8             |

| 12  | 0   | 0    | 5               | 0.8             |

If TTL is used to drive the logic inputs, the V+ supply should be designed to come up before the logic supply, or, current limiting (< 10mA) resistors should be connected in series with the inputs to avoid a potential latch-up condition. Open collector or 74C series logic avoid this problem because of their limited current sourcing capability.

TABLE 2: Channel Decoding

|            |             |             |              |      |     | _ |

|------------|-------------|-------------|--------------|------|-----|---|

| Pin 9<br>C | Pin 10<br>B | Pin 11<br>A | Pin 6<br>INH | СН   | Pin |   |

| 0          | 0           | 0           | 0            | 0    | 13  |   |

| 0          | 0           | •           | 0            | 1    | 14  |   |

| 0          | 1           | 0           | 0            | 2    | 15  |   |

| 0          | 1           | 7           | 0            | 3    | 12  |   |

| 1          | 0           | 0           | 0            | 4    | - 1 |   |

| 1          | 0           | 1           | 0            | 5    | 5   |   |

| 1          | 1           | 0           | 0            | 6    | 2   |   |

| 1          | 1           | 1           | 0            | 7    | 4   |   |

| Х          | X           | X           | 1            | NONE | _   |   |

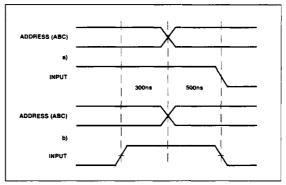

Table 2 shows the channel decoding for the SSM-2300 which is identical to that of 4051 type devices. When there is an address change, it is possible for two or more channels to momentarily be connected to the input at the same time. In order to avoid potential crosstalk problems, either the input signal should be kept at its previous level for 500ns after the address change (Figure 2a) or preferably INH (pin 6) should be exercised as in Figure 2b.

# SUPPLIES (PINS 7, 8, AND 16)

The supply voltages V+ and V- establish the input and output voltage range which is :

V- ≤ inputs, outputs ≤ V+ - 2V

V+ and GND determine the control input logic levels and switch points (see Table 1).

FIGURE 2: Decode Timing

The total supply range is 7 to 15V nominal and 5 to 18V absolute maximum, however, several specifications including acquisition time, offset, and output voltage compliance will degrade for a total supply less than 7V. The positive supply current is typically 4mA with the outputs unloaded. If split supplies are used, the negative supply should be bypassed (i.e., parallel  $0.1 \mu F$  and  $10 \mu F$  capacitors to GND). The hold capacitors are connected to this supply pin and any noise on it will feed through to the outputs.

# SUPPLY SEQUENCING

If TTL logic is used, the SSM-2300 V+ supply should be designed to come up before the logic supply; otherwise current limiting resistors should be connected in series with the logic inputs to prevent latch-up. Resistors should be chosen to limit current below 10mA.

# OUTPUT BUFFERS (PINS 1, 2, 3, 4, 5, 12, 13, 14, AND 15)

The buffer offset specification is ±50mV. This is approximately 1 LSB of an 8-bit DAC with a 10V full scale. The change in offset over the output range is typically 3mV. The hold step (the voltage shift when a channel is deselected) is about 4mV with little variation. The droop rate of a held channel is ±500mV/second typical and ±1500mV/second maximum (input and output(s) at opposite extremes of the voltage compliance range).

The buffers were designed primarily to drive loads connected to ground. The outputs can source more than 1.2mA each over the full voltage output range, but have limited current sinking capability near V—. In split supply operation, symmetrical output swing can be obtained by restricting the output range to 2V from either supply. The output impedance with the output sourcing current is approximately  $0.1\Omega$ . With the output sinking current, the impedance is approximately  $1\Omega$ .

The SSM-2300 buffers eliminate potential stability problems associated with external buffers as the outputs are stable with capacitive loads up to 500pF. However, the SSM-2300 buffer outputs are not short-circuit protected. Care should be taken to avoid shorting any of the outputs to the supplies or ground.

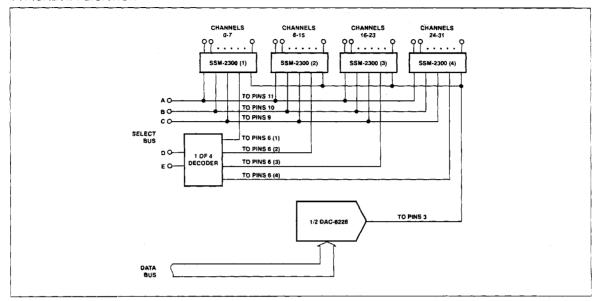

## TYPICAL APPLICATION

## **GENERAL INFORMATION**

## HANDLING

By design consideration, the SSM-2300 gate inputs have a resistor/diode protection network. Inherent P-N junction diodes provide diode protection for all gate inputs and outputs. At the input and output interfaces, the diode networks of the SSM-2300 are protected from gate-oxide failure (70 - 100 volt limit) for static discharge or signal voltages up to 1,000 to 2,000 volts under most transient or low current conditions.

# **OPERATING**

All unused inputs should be connected to either V+ or V- depending on the appropriate logic circuit. For connector-driven inputs which may temporarily become unterminated, a pull-up resistor to V+ or V- should be used with a value ranging from 0.2 to  $1M\Omega$ .

NOTE: Do not apply signals to the SSM-2300 with power off unless the input current's value is limited to less than 10mA.

# **APPLICATIONS**

For signal frequencies near DC, almost any number of SSM-2300s can be connected in parallel; for example, in process control applications this allows a single DAC to service many control channels simultaneously (see Typical Application schematic). The 1µs acquisition time, the number of channels, and the address timing determines the maximum update rate. Sixteen channels of full band audio can be demultiplexed with a single DAC and two SSM-2300s.