# 7-51-09-12 CMOS 12-Bit Monolithic Multiplying DAC

MP7621/7541

#### **FEATURES**

- 12-Bit Linearity (0.01%), achieved without laser trimming of ladder Rs

- Full Four-Quadrant Multiplication

- .5 ppm/°C Gain Error Tempco

- Plug-In Replacement For AD7541 and AD7521

- TTL/CMOS Compatible

- Low Power Consumption

- Low Feedthrough Error

## **APPLICATIONS**

Digital/Synchro Conversion Programmable Amplifiers Ratiometric A/D Conversion Function Generation

#### **GENERAL DESCRIPTION**

The MP7621 is a 12-bit monolithic digital-to-analog converter, featuring high-density CMOS. Precision thin-film deposition allows 12-bit linearity without laser trimming, thus eliminating any long-term instabilities the laser might introduce. Thermal compensation reduces Gain Error Tempco to 2 ppm/°C maximum.

Also, the MP7621 is a pin-compatible replacement for Analog Devices' AD7541. It meets or exceeds the performance of that device, with improved supply rejection, improved temperature stability, lower output glitching, and lower variation of linearity and gain error with VDD.

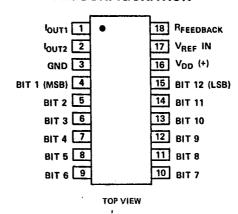

#### **PIN CONFIGURATION**

See Section 7 for Ordering Information

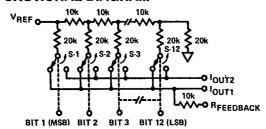

#### **FUNCTIONAL DIAGRAM**

DIGITAL INPUTS (DTL/TTL/CMOS COMPATIBLE)

Logic: A switch is closed to IOUT1 for its digital input in a "high" state.

# MP7621/7541

T-51-09-12

# OPERATING TEMPERATURE RANGE UNLESS OTHERWISE NOTED

| PARAMETER                       | 7621                            | 7541                                   | TEST CONDITION                       |

|---------------------------------|---------------------------------|----------------------------------------|--------------------------------------|

| STATIC ACCURACY                 |                                 |                                        |                                      |

| Resolution                      | 12 bils min.                    | 12 bits min.                           |                                      |

| Nonlinearity                    | ŀ                               | 1 \$ 1                                 |                                      |

| JN, AD, SD                      | ±0.024% FSRI max.               | ±0.024% FSR max.                       | Vourt = Vout2 = 0V                   |

| KN, BD, TD                      | ±0.012% FSR max.                | ±0.012% FSR max.                       | 10011 10012 11                       |

| Nonlinearity Tempeo             | 0.2ppm of FSR. °C max.          | 0.2ppm of FSR/°C max.                  |                                      |

| Gain Error <sup>1, 2</sup>      | ±0.4% FSR max.                  | ±0.4% FSR max.                         |                                      |

| Gain Error Tempco?              | 0.5ppm of FSR.°C typ.           | A of FSB 18G man                       |                                      |

|                                 | 2ppm of FSR;°C max.             | 5ppm of FSR/°C max.                    | VDD = 14.5V - 15.5V 25°C             |

| Power Supply Rejection          | ±.003% per % max.               | ±0.01% per % max.<br>±0.02% per % max. | 400 - 14.54 - 15.54 25°C             |

|                                 | ±.005% per % max.<br>±50nA max. | ±50nA max.                             | VREF = ±10V 25℃                      |

| Quiput Leakage Current          | ±200 nA max.                    | ±200 nA max.                           | THEF - 2101 25 C                     |

|                                 | ±200 IA III.                    | Zadotira intex.                        |                                      |

| DYNAMIC PERFORMANCE             |                                 | l                                      | To 0.012% of FSR                     |

| Output Current Settling Time1   | l μs max.                       | I μs max.                              | VREF = 20V p-p @ 10kHz               |

| Feedthrough Error)              | I mV p-p max.                   | I mV p-p max.                          | AHEL - SOA b-b @ TOKETS              |

| REFERENCE INPUT                 |                                 |                                        |                                      |

| Input Resistance                | 5kΩ min., 20kΩ max.             | 5kΩ min., 20kΩ max.                    | Ì                                    |

| DIGITAL INPUTS                  | 1                               |                                        | i                                    |

| Vinh                            | . 2.4V min.                     | 2,4V min.                              |                                      |

| Vinl                            | 0.8V max.                       | 0.8V max.                              |                                      |

| Input Leakage Current           | ±1 μA max.                      | ±1μA max.                              | ViN = 0 or 15V                       |

| Input Capacitance3              | 8pF max.                        | 8pF max.                               |                                      |

| Input Coding                    | Binary or Offset                | i                                      |                                      |

|                                 | Binary (see page 6)             | 1                                      |                                      |

| ANALOG OUTPUTS                  | l                               | 1                                      |                                      |

| Qutput Capacitance <sup>3</sup> | 52pF max.                       | 52pF max.                              | ł                                    |

| Couti                           | 13pF max.                       | 13pF max.                              | Digital Inputs = VINH                |

| Coutz                           | , .                             | 1 *                                    | 1                                    |

| Couti                           | 26pF max.                       | 26pF max.                              | Digital Inputs = VINL                |

| Conts                           | 45pF max.                       | 45pF max.                              | ,                                    |

| POWER REQUIREMENTS              | 1                               |                                        | Accuracy is guaranteed               |

| Von Range                       | +5V min., +16V max,             | +5V min., +16V max.                    | +10 to +15V, V <sub>p,F</sub> 0.5V   |

|                                 | 1                               | 34                                     | Digital Imputs: V <sub>N</sub> =0.5V |

| 100                             | 2mA max.                        | 2mA max,                               | DiRiter surbare: AM-073A             |

NOTES: FSR is Full Scale Range; Using internal feedback resistor; Guaranteed by design, not subject to test; Specifications subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS**

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| V <sub>DD</sub> (to GND)+17V                |

|---------------------------------------------|

| V <sub>REF</sub> (to GND)                   |

| Digital Input Voltage Range VDD to GND      |

| Output Voltage (Pin 1, Pin 2)300mV to +6.5V |

| Power Dissipation (Package)                 |

| Up to +75°C                                 |

| Derate above +75°C by6mW/°C                 |

| Operating Temperature                       |

| JN, KN Versions 0 to +70°C                  |

| AD, BD Versions25°C to +85°C                |

| SD, TD Versions                             |

| Storage Temperature                         |

#### CAUTION

- Do not apply voltages higher than V<sub>DD</sub> or less than GND potential on any terminal except V<sub>REF</sub>.

- The digital control inputs are zener protected; however permanent damage may occur on unconnected units under high energy electrostatic fields. Keep unused inputs in conductive foam at all times.

#### SPECIFICATION DEFINITIONS

- NONLINEARITY: Error contributed by deviation of the DAC transfer function from a best straight line function. Normally expressed as a percentage of full scale range. For a multiplying DAC, this should hold true over the entire VREF range.

- RESOLUTION: Value of the LSB. For example, a unipolar converter with n bits has a resolution of (2-n) (VREF). A bipolar converter of n bits has a resolution of [2-(n-1)] [VREF]. Resolution in no way implies linearity.

- SETTLING TIME: Time required for the output function of the DAC to settle to within 1/2 LSB for a given digital input stimulus, i.e., 0 to Full Scale.

- GAIN: Ratio of the DAC's operational amplifier output voltage to the input voltage.

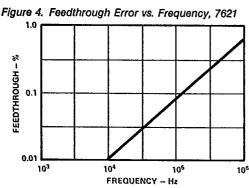

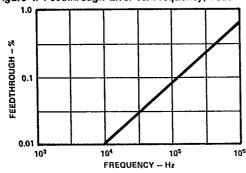

- FEEDTHROUGH ERROR: Error caused by capacitive coupling from VREF to output with all switches OFF.

- OUTPUT CAPACITANCE: Capacity from I<sub>OUT1</sub> and I<sub>OUT2</sub> terminals to ground.

- OUTPUT LEAKAGE CURRENT: Current which appears on IOUT1 terminal with all digital inputs LOW or on IOUT2 terminal when all inputs are HIGH.

1-59

1

30E D

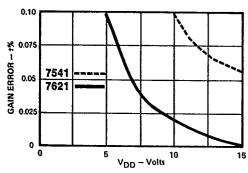

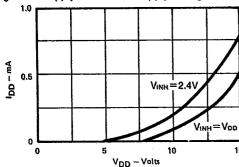

Figure 2. Supply Current vs. Supply Voltage, 7621

10

# APPLICATION HINTS

Linearity depends upon the potential of I<sub>OUT1</sub> and I<sub>OUT2</sub> (pin 1 and pin 2) being exactly equal to GND (pin 3) and the output amplifier's non-inverting (+) input. Careful PC board layout and adjustment and selection of the amplifier's offset voltage and bias current are necessary, any resistance in series with I<sub>OUT2</sub> will degrade linearity at  $I\Omega \cong 0.4$  LSB.

The input structures of some high speed operational amplifiers can attempt to draw substantial current during switch-on. Schottky diodes should be used in these circumstances to prevent the absolute maximum rating for VOUT1 and VOUT2 being exceeded.

The power supply should be carefully checked for noise, which would affect performance, and overshoot which could damage the device.

Unused digital inputs must always be grounded or taken to  $V_{DD}$  to ensure correct operation. Particular care should be taken when digital inputs are routed to another PC card. It is recommended that inputs open-circuited when PC cards are disconnected be taken to  $V_{DD}$  or GND via high value (1M $\Omega$ ) resistors to prevent the accumulation of static charges.

#### CIRCUIT DESCRIPTION

#### GENERAL CIRCUIT INFORMATION

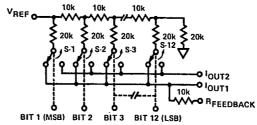

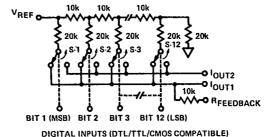

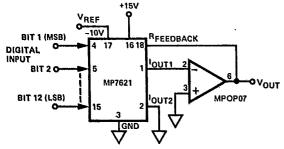

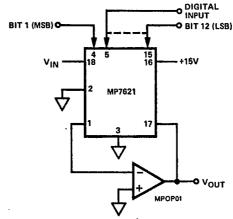

The MP7621, a 12-bit multiplying D/A converter, consists of a highly stable thin film R-2R ladder and twelve CMOS current switches on a monolithic chip. Most applications require the addition of only an output operational amplifier and a voltage or current reference.

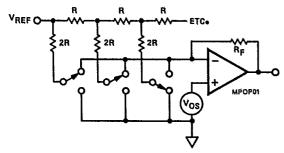

The simplified D/A circuit is shown in Figure 5. An inverted R-2R ladder structure is used—that is, the binarily weighted currents are switched between the IOUT1 and IOUT2 bus lines thus maintaining a constant current in each ladder leg independent of the switch state.

DIGITAL INPUTS (DTL/TTL/CMOS COMPATIBLE)

Figure 5. MP7621 Functional Diagram (Inputs "HIGH")

One of the CMOS current switches is shown in Figure 6. The geometries of devices 1, 2 and 3 are optimized to make the digital control inputs DTL/TTL/CMOS compatible over the full military temperature range. The input stage drives two inverters (devices 4, 5, 6 and 7) which in turn drive the two output N-channels. The "ON" resistances of the switches are binarily scaled so the voltage drop across each switch is the same. For example, switch 1 of Figure 5 was designed for an

20E D

## APPLICATION HINTS

-51-09-12

Linearity depends upon the potential of IOUT1 and IOUT2 (pin 1 and pin 2) being exactly equal to GND (pin 3) and the output amplifier's non-inverting (+) input. Careful PC board layout and adjustment and selection of the amplifier's offset voltage and bias current are necessary, any resistance in series with IOUT2 will degrade linearity at  $1\Omega \cong 0.4 LSB$ .

The input structures of some high speed operational amplifiers can attempt to draw substantial current during switch-on. Schottky diodes should be used in these circumstances to prevent the absolute maximum rating for VOUT1 and VOUT2 being exceeded.

The power supply should be carefully checked for noise, which would affect performance, and overshoot which could damage the device.

Unused digital inputs must always be grounded or taken to VDD to ensure correct operation. Particular care should be taken when digital inputs are routed to another PC card. It is recommended that inputs open-circuited when PC cards are disconnected be taken to  $V_{DD}$  or GND via high value (1M $\Omega$ ) resistors to prevent the accumulation of static charges.

#### CIRCUIT DESCRIPTION

#### GENERAL CIRCUIT INFORMATION

The MP7621, a 12-bit multiplying D/A converter, consists of a highly stable thin film R-2R ladder and twelve CMOS current switches on a monolithic chip. Most applications require the addition of only an output operational amplifier and a voltage or current reference.

The simplified D/A circuit is shown in Figure 5. An inverted R-2R ladder structure is used- that is, the binarily weighted currents are switched between the IOUT1 and IOUT2 bus lines thus maintaining a constant current in each ladder leg independent of the switch state.

Figure 5. MP7621 Functional Diagram (Inputs "HIGH")

One of the CMOS current switches is shown in Figure 6. The geometries of devices 1, 2 and 3 are optimized to make the digital control inputs DTL/TTL/CMOS compatible over the full military temperature range. The input stage drives two inverters (devices 4, 5, 6 and 7) which in turn drive the two output N-channels. The "ON" resistances of the switches are binarily scaled so the voltage drop across each switch is the same. For example, switch 1 of Figure 5 was designed for an

Figure 2. Supply Current vs. Supply Voltage, 7621

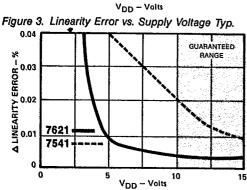

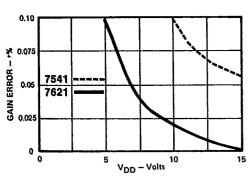

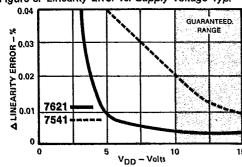

Figure 3. Linearity Error vs. Supply Voltage Typ.

Figure 4. Feedthrough Error vs. Frequency, 7621

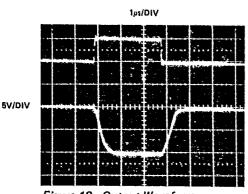

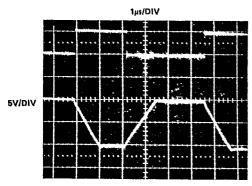

Figure 12. Output Waveform

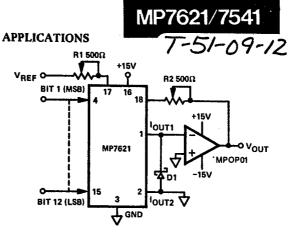

Figure 13. DAC Circuit Using MPOP07

Figure 14. Output Waveform

The circuits and waveforms shown in Figures 9 to 14 are representative of the three types of output amplifiers: a general purpose low drift MPOP02, a high speed low cost MPOP01, and low offset MPOP07.

Points to remember when applying high speed amplifiers include:

- 1. Protection diodes as shown in Figures 15 and 16.

- 2. Phase compensation for the DAC's output capacitance.

- 3. Power supply decoupling and correct load earthing.

Figure 15. Unipolar Binary Operation

#### UNIPOLAR BINARY OPERATION

The connections required for unipolar digital binary operation are shown above. VAEF may be positive or negative so 2-quadrant multiplication may be performed. Schottky diode D1 prevents lours from negative excursions which could damage the device. This precaution is only necessary with certain high speed amplifiers.

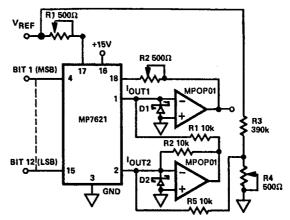

# **BIPOLAR (4-QUADRANT) BINARY OPERATION**

The digital input is offset binary coded and multiplies VREF according to Table 2. Resistors R1 and R2 should be equal within 0.1% at all temperatures, but need not track the resistors within the MP7621. D1 and D2 perform the same function as in Figure 15. Network R3, R4, R5 sum %LSB of current into IOUT2 to ensure correct coding at zero.

R1 or R2 can be adjusted to produce the outputs shown in Table 1. However, it is recommended that when the application permits it R1 and R2 be omitted. The typical gain error in this condition is 0.3% of full scale. The offset voltage of amplifier A1 should be adjusted to less than 0.5mV over the temperature range.

Figure 16. Bipolar (4-Quadrant) Binary Operation

| DIGITAL INPUT | NOMINAL ANALOG OUTPUT     |  |

|---------------|---------------------------|--|

| 111111111111  | -0.99975 V <sub>REF</sub> |  |

| 100000000000  | -0.50000 V <sub>REF</sub> |  |

| 010000000000  | -0.49975 V <sub>REF</sub> |  |

| 000000000000  | o                         |  |

Table 1, Code Table for Circuit of Figure 15.

| DIGITAL INPUT | NOMINAL ANALOG OUTPUT     |  |

|---------------|---------------------------|--|

| 111111111111  | -0.99951 V <sub>REF</sub> |  |

| 100000000001  | -0.00049 V <sub>REF</sub> |  |

| 100000000000  | 0                         |  |

| 010000000000  | +0.50000 V <sub>REF</sub> |  |

| 000000000000  | +1.00000 V <sub>REF</sub> |  |

Table 2. Code Table for Circuit of Figure 16.

Amplifiers A1 and A2 should be adjusted to an input offset of less than 0.1mV and should be better than 0.5mV over the temperature range. With  $V_{REF}$  set to approximately 10V, R4 should be adjusted so that with code 100000000000  $V_{OUT}$  = 0V  $\pm$ 0.2mV. R1 or R2 should be adjusted so that with code 000000000000  $V_{OUT}$  =  $V_{REF}$ .

As with the unipolar circuit R1 and R2 can be omitted, with a resulting typical gain error of 0.3% of full scale. R4 may be replaced by a 100 $\Omega$  fixed resistor. The typical zero error if this is done is 0.015% of F.S.R.

#### **QUTPUT AMPLIFIER CONSIDERATIONS**

It has already been pointed out that the DAC output resistance varies with the digital code. The effect this has on static accuracy will now be considered.

Figure 17.

The error voltage =

$$V_{OS} \left( 1 + \frac{R_F}{R_O} \right)$$

$R_O$  is a function of the digital code,  $R_O\cong 10 \mathrm{k}\Omega$  for any more than 4-bits Logic 1.  $R_O\cong 30 \mathrm{k}\Omega$  for any single bit Logic 1.

The gain for offset, therefore, changes as follows:

At code 001111111111

$$V_{ERROR1} = V_{OS}$$

$\left(1 + \frac{10k}{10k}\right) = 2 V_{OS}$

At code 010000000000  $V_{ERROR2} = V_{OS}$   $\left(1 + \frac{10k}{30k}\right) = \frac{4}{3}V_{OS}$

The error difference is therefore  $\frac{2}{3}$  V<sub>OS</sub>,

Since, for a 12-bit resolution DAC, one LSB has a weight (for  $V_{REF}$  = +10V) of 2.5mV, it is clearly important that  $V_{OS}$  be nulled, either using the amplifier's nulling facility or an external network.

It is important to realize that an offset can be caused by including the usual bias current compensation resistor in the amplifier's non-inverting input terminal. This should not be included. Instead the amplifier should have a bias current which is low over the temperature range of interest, and should certainly not exceed 75nA.

#### ANALOG/DIGITAL DIVISION

Figure 18. Analog/Digital Divider

With the MP7621 connected in its normal multiplying configuration as shown in Figure 15, the transfer function is

$$V_{O} = -V_{IN} \left( \frac{A_{1}}{2^{1}} + \frac{A_{2}}{2^{2}} + \frac{A_{3}}{2^{3}} + \dots + \frac{A_{12}}{A^{12}} \right)$$

where the coefficients  $A_X$  assume a value of 1 for an ON bit and 0 for an OFF bit.

By connecting the DAC in the feedback of an operational amplifier, as shown in Figure 18, the transfer function becomes

$$V_{O} = \left(\frac{-V_{IN}}{\frac{A_{1}}{2^{1}} + \frac{A_{2}}{2^{2}} + \frac{A_{3}}{2^{3}} + \dots + \frac{A_{12}}{A^{12}}}\right)$$

This is division of an analog variable (V<sub>IN</sub>) by a digital word. With all bits off, the amplifier saturates to its bound, since division by zero is not defined. With the LSB (Bit 12) ON, the gain is 4096. With all bits ON, the gain is 1 (±1LSB).

MP7621/7541

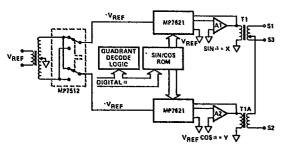

#### DIGITAL/SYNCHRO CONVERTER

Figure 19. 14-Bit Digital to Synchro Converter

The low cost and high accuracy available from the MP7621, together with its bipolar multiplying capability, are exploited fully in the circuit of Figure 19. VREF is commonly 400Hz but by replacing the transformers with de-coupled circuits coordinate transformation may be performed.

The SIN/COS ROM is readily available at low cost and the MP7512 switch enables greater resolution to be obtained.

Resolver-to-synchro transformation is performed by the Scott connected pair T1 and T1A. The power available to the load connected to S1, S2 and S3 is determined by the amplifiers A1 and A2. A particular advantage of the circuit shown in Figure 19 is that it is invariant with respect to  $\theta$ , and may be used to directly drive equipment such as CRT displays.